# phyCORE<sup>®</sup>-LPC3180

## **QuickStart Instructions**

Programming Embedded Linux on phyCORE-LPC3180

Note: The PHYTEC Spectrum CD includes the electronic version of the English phyCORE-LPC3180 Hardware Manual

Edition: June 2007

A product of a PHYTEC Technology Holding company

In this manual are descriptions for copyrighted products that are not explicitly indicated as such. The absence of the trademark ( $^{TM}$ ) and copyright ( $^{\odot}$ ) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is believed to be entirely reliable. However, PHYTEC America LLC assumes no responsibility for any inaccuracies. PHYTEC America LLC neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC America LLC reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages, which might result.

Additionally, PHYTEC America LLC offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC America LLC further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

© Copyright 2007 PHYTEC America LLC, Bainbridge Island, WA.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC America LLC.

|                          | EUROPE                                                                           | NORTH AMERICA                                                                              |

|--------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Address:                 | PHYTEC Technologie Holding AG<br>Robert-Koch-Str. 39<br>D-55129 Mainz<br>GERMANY | PHYTEC America LLC<br>203 Parfitt Way SW, Suite G100<br>Bainbridge Island, WA 98110<br>USA |

| Ordering<br>Information: | +49 (800) 0749832<br>order@phytec.de                                             | 1 (800) 278-9913<br>sales@phytec.com                                                       |

| Technical<br>Support:    | +49 (6131) 9221-31<br>support@phytec.de                                          | 1 (800) 278-9913<br>support@phytec.com                                                     |

| Fax:                     | +49 (6131) 9221-33                                                               | 1 (206) 780-9135                                                                           |

| Web Site:                | http://www.phytec.de                                                             | http://www.phytec.com                                                                      |

2<sup>nd</sup> Edition: June 2007

| 1 | Intr | oductio  | on to the Rapid Development Kit                        | 5    |

|---|------|----------|--------------------------------------------------------|------|

|   | 1.1  | Rapid    | Development Kit Documentation                          | 5    |

|   | 1.2  | Overvi   | ew of this QuickStart Instruction                      | 5    |

| 2 | Sys  | tem De   | scription                                              | 6    |

|   | 2.1  | Rapid    | Development Kit Contents                               | 6    |

|   | 2.2  | Host S   | ystem Requirements for Downloading images (section 3)  | 7    |

|   | 2.3  | Host S   | ystem Requirements for Building new images (section 5) | 7    |

|   | 2.4  | The Pl   | HYTEC phyCORE®-LPC3180                                 | 8    |

|   | 2.5  | LPC31    | 80 Boot Process                                        | 8    |

| 3 | Get  | ting Sta | arted                                                  | 9    |

|   | 3.1  | Installi | ng Rapid Development Kit Software                      | 9    |

|   |      | 3.1.1    | Installing PHYTEC Spectrum CD                          | 9    |

|   |      | 3.1.2    | Install the Segger jlink.exe and J-Link Drivers        | . 10 |

|   | 3.2  | Interfa  | cing the phyCORE®-LPC3180 to a Host-PC                 |      |

|   | 3.3  | Flashir  | ng Images                                              | . 13 |

|   |      | 3.3.1    | Setup                                                  | . 13 |

|   |      | 3.3.2    | Writing Images to Flash                                | . 16 |

| 4 | Exte | ended I  | Demo: USB-Ethernet                                     | . 21 |

|   | 4.1  | Using    | Ethernet                                               | . 21 |

|   | 4.2  | Using    | MMC/SD Card Devices                                    | . 23 |

| 5 | Get  | ting Mo  | re Involved                                            | . 24 |

|   | 5.1  | Tool C   | hain Setup                                             | . 24 |

|   | 5.2  | Buildin  | g SIBL                                                 | . 24 |

|   | 5.3  | Buildin  | g U-Boot                                               | . 25 |

|   | 5.4  | Buildin  | g Linux Kernel                                         | . 26 |

|   | 5.5  | Root F   | ïle System                                             | . 27 |

|   |      | 5.5.1    | Mount the File System                                  | . 27 |

|   |      | 5.5.2    | Add new application program to File System             | 27   |

|   |      | 5.5.3    | Update Loadable Modules                                | . 27 |

|   |      | 5.5.4    | File System Workflow                                   | . 27 |

|   |      |          |                                                        |      |

## **Index of Figures**

| Figure 1: | Default | Jumper  | Settings | of | the | phyCORE | Carrier | Board | with |

|-----------|---------|---------|----------|----|-----|---------|---------|-------|------|

|           | phyCOR  | E-LPC3  | 180      |    |     |         |         |       | 11   |

| Figure 2: | Power C | onnecto | r        |    |     |         |         |       | 12   |

## **1 Introduction to the Rapid Development Kit**

This Rapid Development Kit contains a phyCORE-LPC3180 SBC module mounted on the phyCORE-LPC3180 Carier Board. The phyCORE-LPC3180 Carrier Board contains the I/O connectors as well as any other interface circuitry not provided on the phyCORE module itself. The phyCORE module, combined with the PHYTEC Carrier Board, provides a platform to jump start embedded designs and propel concept to prototype and finished product.

The PHYTEC Rapid Development Kit also contains cables, power supply, printed schematics, applicable evaluation software development tool CDs, and the PHYTEC Spectrum CD. The PHYTEC Spectrum CD-ROM provides this QuickStart guide, complete electronic documentation and demo programs.

## **1.1 Rapid Development Kit Documentation**

This "Rapid Development Kit" (RDK) includes the following documentation on the enclosed "PHYTEC Spectrum for ARM7/9 CD-ROM":

- the PHYTEC phyCORE-LPC3180 Hardware Manual

- LPC3180 controller User's Manuals and Data Sheets

- this QuickStart Instruction

## **1.2 Overview of this QuickStart Instruction**

This QuickStart instruction guide describes how to install, configure, and run Linux on the PHYTEC phyCORE-LPC3180, which utilizes the NXP LPC3180 MCU (ARM926EJ-S core). The QuickStart guide is structured as follows:

- 1) The "*Getting Started*" section describes installation of the Rapid Development Kit software and how to interface the phyCORE-LPC3180 target hardware to a host PC.

- 2) The *"Flashing"* section demonstrates how to download the bootloader and a Linux image into the on-board NAND Flash.

- 3) The "*Extended Demo: USB-Ethenet*" section assists the user to set up a network with the phyCORE-LPC3180 and a USB-to-Ethernet adapter.

## **2** System Description

## 2.1 Rapid Development Kit Contents

The following PHYTEC hardware and software components are included in the phyCORE-LPC3180 Rapid Development Kit (KPCM-031-LINUX) and are necessary for completing the instructions in this application note:

- the PHYTEC phyCORE-LPC3180 (PCM-031) featuring:

- 32MB of NAND Flash

- 32MB of SDR SDRAM

- NXP ISP1301 USB OTG transceiver

- two high-speed RS-232 transceivers supporting three UARTs at up to 460kbps

- the phyCORE-LPC3180 Carrier Board (PCM-976) featuring:

- two RS-232 DB9 Connectors for serial communication to a PC

- USB Host, Device, and OTG connectors for USB connectivity

- JTAG connector

- four user LEDs / two user buttons / one user potentiometer

- one MMC card slot

- keyboard interface

- power connector

- AC adapter supplying 5 VDC /min. 500 mA, center positive

- RS-232 DB9 serial cable

- USB A to B cable

- the Segger J-Link JTAG-USB adapter, only included in the Linux Rapid Development Kit version<sup>1</sup>

- the PHYTEC Spectrum CD for ARM7/9 including kit documentation, Linux BSP source, ARM toolchain, SIBL (secondary bootloader), U-Boot, kernel, and root file system images.

In addition to the kit contents, the following hardware is required for the USB-Ethernet demo:

- A powered USB hub<sup>2</sup>. This document uses a 4-port i-Connect powered USB hub.

- A USB-to-Ethernet adapter. This document uses the SMC Networks Compact USB 2.0 to 10/100 Mbps Ethernet Adapter, part number SMC2209USB/ETH.

<sup>&</sup>lt;sup>1</sup>: The Segger J-LINK is included in the Rapid Development Kit version with the part number KPCM-031-LINUX.

<sup>2:</sup> The phyCORE-LPC3180 is a USB OTG enabled device. When operating as an embedded host, an OTG device can only supply up to 8mA of operating current. Most non-OTG enabled USB devices require more than 8mA of operating current so a powered USB hub is typically required to interface USB devices.

## 2.2 Host System Requirements for Downloading images (section 3)

- Operating System: Windows 2000 or Windows XP

- Terminal emulation program such as HyperTerminal, Terminal or TeraTerm

- One available USB 2.0 or USB 1.1 device port

- One available serial RS-232 COM port (or USB-to-RS-232 adapter)

## 2.3 Host System Requirements for Building new images (section 5)

- Operating System: Linux

- Terminal emulation program such as, Minicom or RealTerm

For more information and example updates, please refer to the following sources:

http://www.phytec.com - or - http://www.phytec.de support@phytec.com - or - support@phytec.de

## 2.4 The PHYTEC phyCORE®-LPC3180

The phyCORE-LPC3180 supports the industry's first 90nm ARM-9 based microcontroller. The new 32-bit MCU high-performance, low power LCP3180 ARM926EJ-S device from NXP Semiconductors (founded by Philips) is the only ARM9 microcontroller that provides a vector floating-point co-processor and integrated USB OTG, as well as the ability to operate in ultra-low-power mode down to 0.9V. The on-board MMU supports many embedded operating systems. Other chip-level features include 7 UARTs, SPI, I<sup>2</sup>C, a real-time clock with a separate power domain, and NAND Flash and DDR memory controllers.

Please refer to the phyCORE-LPC3180 Hardware Manual for specific information on board-level features, jumper configuration, memory mapping, pin layout, and carrier board features.

#### 2.5 LPC3180 Boot Process

The LPC3180 boot process is a multi-staged effort involving one or more boot loaders. After a reset the LPC3180 executes its on-chip bootstrap software located in the on-chip boot ROM. The bootstrap software first looks at the latched value of the GPI\_1/SERVICE\_N signal of the MCU and either (1) copies code from NAND Flash into internal RAM and executes it, or (2) attempts a data download over UART5; if no code is received within the timeout period, booting proceeds from NAND Flash as outlined in (1). Configuration of the boot mode is done via an external jumper on the phyCORE-LPC3180 Carrier Board. By default the Carrier Board should be configured for boot process (2). *Please refer to the PHYTEC phyCORE-LPC3180 hardware manual for details on changing this setting if required.*

When booting from NAND Flash the on-chip bootstrap software copies the boot image located in block 0 of the NAND Flash into internal RAM and executes it. For operation of Linux this boot image must be the SIBL secondary boot loader. SIBL will initialize the SLC NAND controller and SDRAM. After initialization SIBL will scan the NAND Flash for images and executables and load these into memory. The first executable it finds, which in our case is U-Boot, will be executed. U-Boot will then start Linux.

Besides starting Linux, U-Boot (Universal boot loader) is a feature-rich boot loader that can be used to boot Linux in a number of different configurations (from Flash, from TFTP download, etc...) More information on U-Boot can be found on the Internet or by typing **help** in U-Boot.

## **3 Getting Started**

What you will learn with this Getting Started example:

- installing Rapid Development Kit software

- interfacing the phyCORE-LPC3180, mounted on the Carrier Board, to a host-PC using the Segger J-LINK

## 3.1 Installing Rapid Development Kit Software

#### 3.1.1 Installing PHYTEC Spectrum CD

The current version of the PHYTEC Spectrum CD for ARM7/9 does not provide a setup program for automatic installation of the LINUX specific kit contents<sup>1</sup>. You will need to manually copy the demos, manuals, and other support documents for this Rapid Development Kit to your local hard drive.

- Insert the PHYTEC Spectrum CD into the CD-ROM drive of your host-PC. The PHYTEC Spectrum CD should automatically launch a setup program.

- Please exit the installation screen.

- Open a Windows Explorer (or similar program) and browse to the *PHYBasic\pC-LPC3180* folder on the PHYTEC Spectrum CD-ROM.

The *pC-LPC3180* folder within *PHYBasic* contains the following directories:

- The *Quickstart* folder contains this QuickStart document *L-698e\_1.pdf*

- The *Linux* folder contains the ARM Linux tool chain, Linux BSP source code, file system, Linux BSP documentation from NXP, and demo images required for this QuickStart.

- The *Manual* folder contains the phyCORE-LPC3180 Hardware Manual

Copy the three folders listed above to your local hard drive in a location named *C:\PHYBasic\pC-LPC3180*. Make sure to remove the read-only attribute from all files copied to you hard drive.

**Note:** All path and file statements within this QuickStart Instruction are based on the assumption that you choose *C:\PHYBasic\pC-LPC3180* as the default path when copying files from the Spectrum CD-ROM to your hard drive.

<sup>&</sup>lt;sup>1</sup>: Future versions of the Spectrum CD will offer automatic installaion for LINUX kit contents in the same manner as currently available for KEIL and IAR kit versions.

#### 3.1.2 Install the Segger jlink.exe and J-Link Drivers

The Segger J-Link includes a CD-ROM with the required Windows drivers and the *jlink.exe* command prompt utility. In addition PHYTEC provides the most recent version (as of the printing of this manual) of the J-Link drivers on the Spectrum CD for ARM7/9. Alternatively you can download recent<sup>1</sup> USB the most J-Link driver from Segger at the following URL: http://www.segger.com/download\_jlink.html.

It is important that you use the most recent version of the Segger J-Link drivers. PHYTEC recommends installing the J-Link driver and jlink.exe from the Spectrum CD for ARM7/9.

- In a Windows Explorer (or similar program) browse to the C:\PHYBasic\pC-LPC3180\Segger folder (or the same location on the PHYTEC Spectrum CD-ROM) and run the file Setup\_JLinkARM\_V368b.exe.

- Follow the installation steps on the screen.

- Once the installation is complete jlink.exe can be found at the following installation location: C:\Program Files\Segger\JLinkARM\_V368b. jlink.exe will be required for flashing images as described in section 3.3 of this QuickStart manual.

<sup>&</sup>lt;sup>1</sup> At the date this document was released Segger J-Link version 368b was most current.

## 3.2 Interfacing the phyCORE®-LPC3180 to a Host-PC

Connecting the phyCORE-LPC3180, mounted on the phyCORE Carrier Board, to your computer is simple.

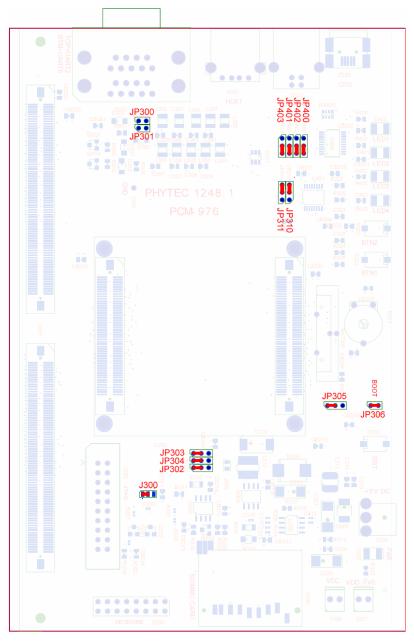

• Ensure proper jumper settings on the phyCORE Carrier Board as shown in *Figure 1*. All phyCORE-LPC3180 Carrier Board jumper settings can be referenced in the phyCORE-LPC3180 Hardware Manual section 13.1.1.

Figure 1: Default Jumper Settings of the phyCORE Carrier Board with phyCORE-LPC3180

- If not pre-mounted. Mount the phyCORE module, pins-down, onto the Carrier Board's receptacle footprint (X200). Ensure that pin 1 of the module, designated by the hash stencil mark, matches pin 1 of the receptacle on the Carrier Board.

- **Note:** Ensure that there is a solid connection between the module's pins and the Carrier Board receptacle. Also take precautions not to damage the connectors when the phyCORE module is removed from and inserted onto the Carrier Board.

- Connect the JTAG-end of the J-Link JTAG probe to the JTAG connector on your phyCORE-LPC3180 Carrier Board. Connect the host (USB) end of the J-Link JTAG probe to an available USB port on your host computer. The J-Link JTAG tool is used to download images to the phyCORE-LPC3180 board.

- Connect the RS-232 interface on the host PC to the bottom connector of the UART interface (UART5) on the phyCORE<sup>®</sup> Carrier Board using the included serial cable.

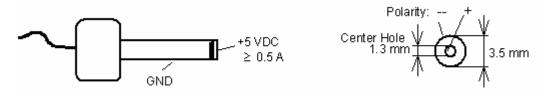

- Connect the included 5V power adapter to the power socket X304 on the phyCORE Carrier Board (refer to Figure 2 for the correct polarity).

Figure 2: Power Connector

• The red power LED D307, located next to the power socket at X304, should illuminate. This indicates that proper voltage is supplied to the phyCORE module/Carrier Board combination (which is also referred to as "target hardware" within this document).

The phyCORE module/Carrier Board combination should now be properly connected to a host PC via the Segger J-LINK.

## 3.3 Flashing Images

Flashing images on the phyCORE-LPC3180 involves using one or both of the NAND Flash controllers available on the LPC3180. Both the SLC and MLC NAND Flash controllers on the LPC3180 can be used to write to the SLC NAND Flash device populating the phyCORE-LPC3180. Special attention should be paid to which Flash controller is being used when writing to NAND Flash. Because of error correction code incompatibility, data is incompatible between the two NAND controllers; data written by one controller is not readable by the other, and vice-versa.

Currently the *Bootflash* utility written by PHYTEC is used to flash all images to the phyCORE-LPC3180 NAND Flash. Bootflash uses the MLC NAND controller to write the secondary boot loader SIBL, while the Linux kernel, Linux file system, and U-Boot images are written using the SLC NAND controller.

Bootflash will be loaded into RAM and executed to make use of its command prompt driven interfaces for Flash manipulation. The basic flashing procedure is as follows:

- An instance of Bootflash will be first downloaded via the J-Link to the LPC3180 internal RAM and execution will be transferred to the downloaded Bootflash instance.

- SIBL, U-Boot, the Linux kernel, and the Linux file system will be downloaded into SDRAM.

- Two Bootflash commands will be issued to burn the images stored in SDRAM into NAND Flash.

#### 3.3.1 Setup

#### 3.3.1.1 Environment Path

Begin by setting up your environment path variable to point to the location of the **jlink.exe**.

- Right-click on the *My Computer* icon on your desktop and choose *Properties*.

- Click on the *Advanced* tab and click on the *Environment Variables* button. If the **PATH** variable exists append a new path at the end in the format PATH1;PATH2. If it does not exist click **New** to create a new user variable.

- Name this new variable **PATH**. The *Variable value* needs to be the location of the **jlink.exe**, which for the purposes of this document is in:

| C:\Program Files\ | SEGGER\JLinkA                                     | RM_V368b                                              |

|-------------------|---------------------------------------------------|-------------------------------------------------------|

|                   | Edit User Variable                                | ? 🗙                                                   |

|                   | Variable <u>n</u> ame:<br>Variable <u>v</u> alue: | PATH C:\Program Files\SEGGER\JLinkARM_V368b OK Cancel |

• Click OK to close the New User Variable, Environment Variables, and System Properties windows.

#### 3.3.1.2 Terminal Program

Create a new connection with a Terminal program such as HyperTerminal, indicate the correct COM settings for Host System and set the parameters as follows: Bits per second = 115200; Data bits = 8; Parity = None; Stop bits = 1; Flow control = None.

| Bits n | er second:  | 115200 |    | -        |

|--------|-------------|--------|----|----------|

| Dicop  | or second.  | 110200 |    |          |

|        | Data bits:  | 8      |    | -        |

|        | Parity:     | None   |    | •        |

|        | Stop bits:  | 1      |    | •        |

| Flo    | ow control: | None   |    | <b>_</b> |

|        |             |        | 14 |          |

#### 3.3.1.3 Command Prompt

Open a command prompt window and browse to the *Demo* folder at this location: C:\PHYBasic\pC-LPC3180\Linux\Demo

| 🗪 Command Prompt                          |                                  |                                      |   |

|-------------------------------------------|----------------------------------|--------------------------------------|---|

| C:\PHYBasic\pC-LPC318                     |                                  |                                      |   |

| bootflash.bin                             | rootfs_phytec.ubt                | uImage_phytec.ubt                    |   |

| load_bootflash.jlink<br>load_images.jlink | sibl_phytec.bin<br>uImage_phytec | uboot_phytec.bin<br>uboot_phytec.ubt |   |

| C:\PHYBasic\pC-LPC318                     | 0\Linux\Demo>_                   |                                      |   |

|                                           |                                  |                                      |   |

|                                           |                                  |                                      |   |

|                                           |                                  |                                      | • |

You should see the following files:

| bootflash.bin        | rootfs_phytec.ubt | uimage_phytec.ubt |

|----------------------|-------------------|-------------------|

| load_bootflash.jlink | sibl_phytec.bin   | uboot_phytec.bin  |

| load_images.jlink    | ulmage_phytec     | uboot_phytec.ubt  |

#### 3.3.2 Writing Images to Flash

To boot Linux from phyCORE-LPC3180 NAND Flash, four images must be written to the NAND Flash: (1) SIBL, (2) U-Boot, (3) the Linux image, and (4) the Linux file system. The Bootflash utility is used to burn these images to NAND Flash.

Return to the command prompt window where you have placed the images. Execute the load\_bootflash.jlink script by typing the following command:

```

C:\PHYBasic\pC-LPC3180\Linux\Demo>jlink load_bootflash.jlink

🗪 Command Prompt - jlink load_bootflash.jlink

_ 🗆 🗙

C:\PHYBasic\pC-LPC3180\Linux\Demo>jlink load_bootflash.jlink

SEGGER J-Link Commander V3.68b ('?

for help)

Compiled Mar 30 2007 16:52:53

DLL version V3.68b, compiled Mar 30 2007 16:52:49

Firmware: J-Link compiled Mar 22 2007 16:08:22 ARM Rev.5

Hardware: U5.20

S/N : 10005747

OEM : IARKS

VTarget = 2.983V

JTAG speed: 30 kHz

Info: CP15.0.0: 0x41069264: ARM, Architecure 5TEJ

Info: CP15.0.1: 0x10022192: ICache: 32kB (4×256×32), DCache: 32kB (4×256×32)

Found 2 JTAG devices, Total IRLen = 8:

Id of device #0: 0x1B900F0F

Id of device #1: 0x17900F0F

ound ARM with core Id 0x17900F0F (ARM9)

ETM UI.3: 8 pairs addr.comp, 8 data comp, 16 MM decs, 4 counters, sequencer

ETB UI.0: 2048x24 bit RAM

Script file read successfully.

Processing script file...

Reset delay: 0 ms

Reset type NORMAL: Using RESET pin, halting CPU after Reset

Info: Resetting target using RESET pin

Info: J-Link: ARM9 CP15 Settings changed: 50078 from 78, MMU Off, ICache Off, DC

ache Off

Info: CP15.0.0: 0x41069264: ARM, Architecure 5TEJ

Info: CP15.0.1: 0x1D192192: ICache: 32kB (4*256*32), DCache: 32kB (4*256*32)

JTAG speed: 1000 kHz

Loading binary file... [bootflash.bin]

Writing bin data into target memory @ 0x08000000.

Script processing completed.

J-Link>_

```

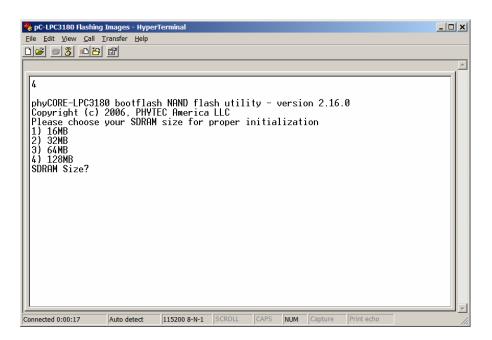

• Return to the HyperTerminal window. You should see the output from the Bootflash utility.

Select 2 from the menu for the default 32 MB SDRAM populating the phyCORE-LPC3180 Linux development kits. If you have SDRAM of a different size, please select accordingly.

|                                                                                                                                                                                                                                                                                                                                                   | <u>_     ×</u> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| File Edit View Call Transfer Help                                                                                                                                                                                                                                                                                                                 |                |

| <u>DF 3 08 6</u>                                                                                                                                                                                                                                                                                                                                  |                |

| 4<br>phyCORE-LPC3180 bootflash NAND flash utility - version 2.16.0<br>Copyright (c) 2006, PHYTEC America LLC<br>Please choose your SDRAM size for proper initialization<br>1) 16MB<br>2) 32MB<br>3) 64MB<br>4) 128MB<br>SDRAM Size? 2<br>Initialized SDRAM interface for 32MB<br>SI Micro - 256Mbit (32MByte) NAND Flash detected<br>bootflash \$ |                |

| Connected 0:00:34 Auto detect 115200 8-N-1 SCROLL CAPS NUM Capture Print echo                                                                                                                                                                                                                                                                     |                |

Now return to the command prompt window and quite the Jlink program by entering q in the command prompt

J-Link>q

© PHYTEC America LLC 2007 L-698e\_2

• Execute the load\_images.jlink script by typing the following command:

```

C:\PHYBasic\pC-LPC3180\Linux\Demo>jlink load_images.jlink

```

The script will take one to two minutes to complete execution. Once the script is complete the images (uboot\_phytec.ubt, ulmage\_phytec.ubt, rootfs\_phytec.ubt, sibl\_phytec.bin) will be loaded into the SDRAM.

| 🚥 Command Prompt - jlink load_images.jlink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _ 🗆 🗙 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| JTAG speed: 30 kHz<br>Info: CP15.0.0: 0x41069264: ARM, Architecure 5TEJ<br>Info: CP15.0.1: 0x1D192192: ICache: 32kB (4×256×32), DCache: 32kB (4×256×32<br>Found 2 JTAG devices, Total IRLen = 8:<br>Id of device #0: 0x1B900F0F<br>Id of device #1: 0x17900F0F<br>Found ARM with core Id 0x17900F0F (ARM9)<br>ETM V1.3: 8 pairs addr.comp, 8 data comp, 16 MM decs, 4 counters, sequenc<br>ETB V1.0: 2048x24 bit RAM                                                                                                                                                                                                                                                                                                                                                         |       |

| Script file read successfully.<br>Processing script file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| JTAG speed: 1000 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| <pre>PC: (R15) = 00004CC8, CPSR = 600000DF (System mode, ARM FIQ dis. IRQ dis.)<br/>R0 = 00000060, R1 = 0000005, R2 = 00000014, R3 = 00000012<br/>R4 = 00008C44, R5 = 00000144, R6 = 00000000, R7 = 00000130<br/>USR: R8 =00C65D40, R9 =CA31E000, R10=0C003FFC, R11 =00000034, R12 =00000000<br/>R13=0000AE44, R14=00003B50<br/>FIQ: R8 =C12C2430, R9 =81FA78A1, R10=C90253F0, R11 =973E3F91, R12 =53D6039B<br/>R13=37F2977D, R14=F1BF902C, SPSR=00000010<br/>SUC: R13=0000F5F0, R14=0C0001BC, SPSR=00000010<br/>ABT: R13=566B9B23, R14=3A82C289, SPSR=00000010<br/>IRQ: R13=0000AF58, R14=94E47009, SPSR=00000010<br/>UND: R13=82C491A8, R14=C30722AD, SPSR=00000010<br/>Loading binary file [uboot_phytec.ubt]<br/>Writing bin data into target memory @ 0x80900000.</pre> |       |

| Loading binary file [uImage_phytec.ubt]<br>Writing bin data into target memory @ 0x80600000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| Loading binary file [rootfs_phytec.ubt]<br>Writing bin data into target memory @ 0x80000000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| Loading binary file [sibl_phytec.bin]<br>Writing bin data into target memory @ 0x81000000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Script processing completed.<br>J-Link>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

- After the script completes, return to the HyperTerm window and the running instance of Bootflash.

- Now that the images are in SDRAM they can be written to the on-board NAND Flash. At the Bootflash command prompt issue the following command:

bootflash \$ lflash

Once the Jflash command is executed Bootflash will begin by scanning the SDRAM for **.ubt** files that were loaded in the **jlink load\_images.jlink** step. If all files were found successfully, and the data is error free Bootflash will continue by calculating the available space in the NAND Flash and comparing this to the size of the images. If enough space is available Bootflash will erase a new area for each image, followed by programming the images into the newly erased areas. Note that Bootflash will skip any bad blocks currently existing in Flash during the write process. See below for reference:

| 🗞 pC-LPC3180 Flashing Images - HyperTerminal                                                                                                                                                                                                                                    | _ 🗆 X |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Elle Edit View Call Iransfer Help                                                                                                                                                                                                                                               |       |

|                                                                                                                                                                                                                                                                                 |       |

|                                                                                                                                                                                                                                                                                 |       |

| Searching for U-Boot<br>Found: My U-Boot v0.1 @ 0x80900000                                                                                                                                                                                                                      |       |

| Searching for the Linux Kernel<br>Found: Linux-2.6.10 @ 0x80600000                                                                                                                                                                                                              |       |

| Searching for the Linux Filesystem<br>Found: My RootFS v0.1 @ 0x80000000                                                                                                                                                                                                        |       |

| Calculating available space<br>Space requirement is OK!                                                                                                                                                                                                                         |       |

| Erasing an area for the Linux File System - 100%<br>Writing the Linux File System @ 0x00004000 - 100%<br>Erasing an area for the Linux Kernel - 100%<br>Writing the Linux Kernel @ 0x00450000 - 100%<br>Erasing an area for U-Boot - 100%<br>Writing U-Boot @ 0x0052c000 - 100% |       |

| U-Boot was placed @ NAND addr 0x0052c000, spanning 10 blocks<br>Linux Kernel was placed @ NAND addr 0x00450000, spanning 55 blocks<br>Linux File System was placed @ NAND addr 0x00004000, spanning 275 blocks<br>bootflash \$                                                  |       |

|                                                                                                                                                                                                                                                                                 |       |

| Connected 0:28:25 Auto detect 115200 8-N-1 SCROLL CAPS NUM Capture Print echo                                                                                                                                                                                                   |       |

Next the secondary boot loader SIBL must be written to Flash. The load\_images script placed this file at the SDRAM address 0x81000000. To write this binary file to Flash, the command **nand bwrite** must be used. Type the following command at the Bootflash prompt:

bootflash \$ nand bwrite 0x81000000 0x1400

| ile Edit View Call                                                                                                                                                  |                                                                                                                           |                                                                                 |                        |          |       |       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------|----------|-------|-------|--|

| Erasing an are                                                                                                                                                      | ea fo <mark>r</mark> U-Boo                                                                                                | ot - 100%                                                                       |                        |          |       |       |  |

| Writing U-Boo<br>U-Boot was pla<br>Linux Kernel v<br>Linux File Svs                                                                                                 | aced @ NAND<br>was placed @                                                                                               | addr 0x00<br>NAND add                                                           | 52c000, s<br>r 0x00451 | 0000, sj | janni | ng 55 |  |

| bootflash \$ ne<br>Frasing BLOCK<br>Writing boot of<br>Copying data<br>Data written<br>Data written<br>Data written<br>Data written<br>Data written<br>Data written | 0<br>lata into bl<br>to block 0<br>to block 0,<br>to block 0,<br>to block 0,<br>to block 0,<br>to block 0,<br>to block 0, | ock Ø, pa<br>page 1<br>page 2<br>page 3<br>page 4<br>page 5<br>page 6<br>page 7 |                        |          |       |       |  |

| Data written<br>Data written<br>Data written<br>Data written<br>Operation com                                                                                       | to block Ø,<br>to block Ø,                                                                                                | page 9<br>page 10                                                               |                        |          |       |       |  |

| Data written<br>Data written<br>Data written                                                                                                                        | to block Ø,<br>to block Ø,                                                                                                | page 9<br>page 10                                                               |                        |          |       |       |  |

© PHYTEC America LLC 2007 L-698e\_2

All required images have been written to the NAND Flash. Upon a hardware reset the Linux image should begin booting.

- Press the reset button, labeled "RST", located near the 5V power connector on the phyCORE-LPC3180 Carrier Board. Linux will begin booting.

- After successful boot, Linux login prompt should display:

| 🏀 LPC3180 - HyperTerminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ 🗆 🗙 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| File Edit View Call Transfer Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| Scanning device for bad blocks         Bad eraseblock 850 at 0x00d48000         Creating 1 MTD partitions on "NAND 32MiB 1,8V 8-bit":         0x0100000-0x01f00000 : "LPC3180 NAND PART 0"         CSLIP: code copyright 1989 Regents of the University of California         PPP generic driver version 2.4.2         PPP Deflate Compression module registered         PPP BSD Compression module registered         mmc-lpc3180: mmc/sd driver running on platform=lpc3180         : MMCI rev 0 cfg 00 at 0x20098000 irq 15.13         JFFS2 version 2.2. (NAND) (C) 2001-2003 Red Hat, Inc.         Installing knfsd (copyright (C) 1996 okir@monad.swb.de).         running on [console=ttys0,1152000R root=/dev/ram initrd=0x80800000,12M]         Mounting SD/USB storage         No USB storage or unknown filesystem         No USB storage or unknown filesystemid = 1         INIT: Entering runlevel: 2         Creating the the /var/dev/ttySA* links         Starting internet superserver: inetd.         Cinco de Mayo - ARM Embedded Linux version 1.1-vfp         Saturday 05 May 2007 @ 14:00         (none) login: _ |       |

| Connected 0:00:44 ANSIW 115200 8-N-1 SCROLL CAPS NUM Capture Print echo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -//   |

## 4 Extended Demo: USB-Ethernet

This section demonstrates the use of a USB to Ethernet adapter in order to allow networking with the phyCORE-LPC3180. In this demo the USB OTG Linux driver will put the LPC3180 USB controller into host mode. Basic Ping functionallity will be demonstrated.

This demo was completed using the following hardware:

- A powered USB hub<sup>1</sup>. This document uses a 4-port i-Connect powered USB hub.

- A USB-to-Ethernet adapter. This document uses the SMC Networks Compact USB 2.0 to 10/100 Mbps Ethernet Adapter, part number SMC2209USB/ETH.

## 4.1 Using Ethernet

This demo was completed using the following hardware:

- An SMC Networks Compact USB 2.0 to 10/100 Mbps Ethernet Adapter part number SMC2209USB/ETH

- **Note:** USB Host is supposed to output 5V on the "VBUS" pin of the USB connector. This pin is connected to the VBUS pin of the ISP1301 transceiver on the PHYTEC board. When the proper bit in a configuration register on the ISP1301 is set it will then drive the VBUS pin to 5V. This is required for proper host mode operation. Currently the USB OTG driver provides a "software workaround" by temporarily switching the mode of the OTG driver into host mode so the transceiver is operating as host. However, this FORCED host mode does not drive VBUS to 5V. Currently the OTG drivers are configured to drive VBUS to 5V when the USB\_ID pin is grounded.

- Ensure that jumper JP307 on the Carrier Board is closed. This will set USB\_ID to GND

- Ensure that jumper JP308 on the Carrier Board is set to 1+2 for use with a USB hub, or 2+3 with no USB hub connected.

Note that by plugging in this USB hub, powering it up, and plugging in the SMC USB-to-Ethernet adapter **before** powering up the phyCORE-LPC3180 Carrier Board Linux will have automatically detected the USB hub and the SMC USB-to-Ethernet adapter attached to the board during boot up. Optionally you could plug the USB hub + USB-to-Ethernet adapter in after boot up. You will see Linux automatically detect these devices.

- Return to the HyperTerminal window (see section 3.3.2).

- Begin by logging into Linux as "root".

(non) login: root

<sup>1:</sup> The phyCORE-LPC3180 is a USB OTG enabled device. When operating as an embedded host, an OTG device can only supply up to 8mA of operating current. Most non-OTG enabled USB devices require more than 8mA of operating current so a powered USB hub is typically required to interface USB devices.

- Change the directory as follows:

- ~ # cd /sys/devices/platform/container-dev-1

- Force the USB OTG mode to host with the following command:

/sys/devices/platform/container-dev-1 # echo > forced\_mode host

Before the USB-to-Ethernet adapter can be used, it must be configured. An IP address needs to be assigned to the eth0 device using the **ifconfig** command. **The selected IP address must be one available from the pool of local IP addresses on your network.** If you are unsure of proper settings, please consult your network administrator.

• Configure the USB-to-Ethernet IP settings:

~ # ifconfig eth0 192.168.3.122

To access the outside world (other than your local network) execute the route command as follows:

~ # route add -net default gw 192.168.3.254 dev eth0

**Note**: The default gateway IP address is also specific to your network. If you are unsure of proper settings, please consult your network administrator.

• Test the network connection using the ping command (a local IP address on this network):

~ # ping 192.168.3.120

If you have successfully setup the default gateway, you should be able to ping an outside IP address, such as PHYTEC's IP address:

~ # ping 72.34.40.39

Press CTRL+C to abort pinging after verifying that packets are being sent and received.

🏶 pC-LPC3180 Flashing Images - HyperTerminal \_ 🗆 🗙 <u>File Edit View Call Transfer Help</u> 🎦 🖆 🔏 👘 🎦 /sys/devices/platform/container-dev-1 # route add -net default gw 192.168.3.254 dev eth0 /sys/devices/platform/container-dev-1 # ping 192.168.3.120 PING 192.168.3.120 (192.168.3.120): 56 data bytes 64 bytes from 192.168.3.120: icmp\_seq=0 ttl=64 time=12.4 ms 64 bytes from 192.168.3.120: icmp\_seq=1 ttl=64 time=1.4 ms 64 bytes from 192.168.3.120: icmp\_seq=2 ttl=64 time=1.6 ms 64 bytes from 192.168.3.120: icmp\_seq=3 ttl=64 time=1.7 ms 64 bytes from 192.168.3.120: icmp\_seq=4 ttl=64 time=1.7 ms 64 bytes from 192.168.3.120: icmp\_seq=5 ttl=64 time=1.8 ms 64 bytes from 192.168.3.120: icmp\_seq=5 ttl=64 time=1.8 ms 64 bytes from 192.168.3.120: icmp\_seq=6 ttl=64 time=1.9 ms --- 192.168.3.120 ping statistics ---7 packets transmitted, 7 packets received, 0% packet loss round-trip min/avg/max = 1.4/3.2/12.4 ms /sys/devices/platform/container-dev-1 # ping 72.34.40.39 PING 72.34.40.39 (72.34.40.39): 56 data bytes 64 bytes from 72.34.40.39: icmp\_seq=0 ttl=53 time=73.1 ms 64 bytes from 72.34.40.39: icmp\_seq=1 ttl=53 time=70.0 ms --- 72.34.40.39 ping statistics ---2 packets transmitted, 2 packets received, 0% packet loss round-trip min/avg/max = 70.0/71.5/73.1 ms /sys/devices/platform/container-dev-1 # 115200 8-N-1 SCROLL Connected 16:58:29 ANSIW CAPS NUM Capture Print echo

You have now successfully demonstrated use of a USB-Ethernet adapter within the Linux operating system environment. PHYTEC is currently working on instructions for building the Linux kernel and file system using the source BSP provided on the PHYTEC Spectrum CD. Please visit the following PHYTEC product page for additional and updated documentation:

http://www.phytec.com/products/sbc/ARM-XScale/phyCORE-ARM9-LPC3180.html

## 4.2 Using MMC/SD Card Devices

When an SD card is inserted prior to boot time, Linux will automatically detect that and try to mount the device. An SD card must be mounted manually if inserted after Linux has booted.

mount SD card

```

% mount -t auto /dev/mmcblk0 /mnt/mmc

```

## 5 Getting More Involved

What you will learn with this Getting More Involved section:

- Note on SIBL.

- How to build U-Boot.

- How to build the Linux Kernel.

- How to modify the existing root file system and build one from scratch.

- Building a JFFS2 file system.

- How to add user applications.

## 5.1 Tool Chain Setup

A Linux system with root access is necessary for the following sections (with exception to section 5.2)

**Note:** To use a newer version compiler, pay attention that the kernel and the libraries in the root filesystem are built with the same compiler.

Copy the Arm Linux GCC toolchain arm-linux-gcc-2004-q1-vfp.tar.gz from the PHYTEC Spectrum CD: phyBASIC\pC-LPC3180\Linux\Arm to your host machine. The remainder of this Quickstart guide assumes that the path for the Arm toolchain on the host machine is /usr/local/arm/gnu.

## 5.2 Building SIBL

A Windows Sytem with CYGWIN, the ARM RealView tool-suite, and the ARM Realview ICE JTAG Interface adapter is required to build SIBL. It is recommended that the default SIBL be used.

Using the sources in CD: phyBASIC\pC-LPC3180\Linux\BSP Source\sibl, run the make file to generate the files si\_phytec.axf and sible\_phytec.bin :

```

% make clean

```

```

% make phytec

```

#### 5.3 Building U-Boot

- To build U-Boot, the Arm Linux GCC toolchain must be copied to the Linux host machine as described in *section 5.1*.

- Copy the U-Boot files u-boot-1.1.1.tar.gz and u-boot-1.1.1-phytec3180.patch.gz from the PHTYEC Spectrum CD: phyBASIC\pC-LPC3180\Linux\BSP Source\uboot to your host machine. The remainder of this Quickstart guide assumes that the path for uboot and the patch on the host machine is /usr/local/arm/uboot.

- Create a path for make and mkimage executable functions and set the following environment veriables:

```

% export PATH=$PATH:/usr/local/arm/gnu/release-3.4.0-

vfp/bin:/usr/local/arm/uboot/u-boot-1.1.1/tools

```

- % export ARCH=arm

- % export CROSS\_COMPILE=arm-linux-

#### Untar the U-Boot source:

```

% tar -zxvf u-boot-1.1.1.tar.gz

```

• Move patch gz to u-boot-1.1.1

```

% mv ./u-boot-1.1.1-phytec8180.patch.gz ./u.boot-1.1.1

```

• Apply patch:

```

% cd u.boot-1.1.1

```

```

% gzip -cd u-boot-1.1.1-phytec3180.patch.gz | patch -pl

```

- In the u.boot-1.1.1 directory run:

- % make distclean

- % make phytec\_config

- % make

- % make u-boot.axf

The U-Boot files can be converted into a U-Boot image (single line):

```

% ./tools/mkimage -A arm -O u-boot -T Firmware -C none -a

81EC0000 -e 81EC0000 -n "PHYTEC U-Boot v0.1" -d u-boot.bin

uboot_phytec.ubt

```

```

© PHYTEC America LLC 2007 L-698e_2

```

### 5.4 Building Linux Kernel

- To build a Kernel image, the Arm Linux GCC toolchain must be copied to the Linux host machine as described in section 5.1.

- Copy the phyCORE-LPC3180 Linux kernel patch linux-2.6.10-phytec3180.patch.gz from the PHYTEC Spectrum CD: phyBASIC\pC-LPC3180\Linux\BSP Source\kernel to your host machine. The remainder of this Quickstart guide assumes that the path for the kernel patch on the host machine is /usr/local/arm/kernel.

- Download the official Kernal Version 2.6.10 linux-2.6.10.tar.gz from: http://www.kernel.org/pub/linux/kernel/v2.6/ and copy to your host machine. The remainder of this Quickstart guide assumes that the path for the kernel on the host machine is /usr/local/arm/kernel.

- Create a path for **make** and **mkimage** executable functions and set the following environment veriables:

```

% export PATH=$PATH:/usr/local/arm/gnu/release-3.4.0-

vfp/bin:/usr/local/arm/uboot/u-boot-1.1.1/tools

```

% export ARCH=arm

```

% export CROSS_COMPILE=arm-linux-

```

• Untar the kernel source:

```

% tar -zxvf linux-2.6.10.tar.gz

```

• Apply patch to create the LPC3180 ARM Kernel:

```

% cd linux-2.6.10

```

```

% gzip -cd linux-2.6.10-phytec3180.patch.gz | patch -pl

```

• In the linux-2.6.10 directory run:

```

% make clean

```

```

% make lpc3180_deconfig

```

```

% make

```

- % make uImage

- The ulmage file can be converted into a kernel ubt image:

```

% mkimage -A arm -O Linux -T Kernel -C none -a 80600000 -e

80600000 -n "PHYTEC Linux-2.6.10" -d uImage uImage_phytec.ubt

```

## 5.5 Root File System

#### 5.5.1 Mount the File System

- Copy the phyCORE-LPC3180 ext2 root file system root\_fs\_arm.ext2.phytec.gz from the PHYTEC Spectrum CD: phyBASIC\pC-LPC3180\Linux\File System to your host machine. The remainder of this Quickstart guide assumes that the path for the phyCORE-LPC3180 ext2 root file system on the host machine is /usr/local/arm/rootfs.

- Create a directory to mount the root file system.

% mkdir mnt\_rootfs /usr/local/arm/

• Unzip and mount root\_fs\_arm.ext2.phytec::

% gzip -d root\_fs\_arm.ext2.phytec.gz % mount -o loop root\_fs\_arm.ext2.phytec ./mnt\_rootfs

Now it is possible to make modifications to the root file system. Below are instructions for adding a user application, updating loadable modules, and modifying network settings.

#### 5.5.2 Add new application program to File System

• To add a new application program, copy the application to ./mnt\_rootfs:

```

% cp ~apps/hello ~/mnt_rootfs/bin

```

#### 5.5.3 Update Loadable Modules

• When a completely new kernel is built with loadable modules, use the following script to copy the modules to ./lib/modules:

% //collect\_modules

• Copy the new module files to the root file systme:

```

% cp -dpR //lin/modules/2.6.10/kernel

~/mnt_rootfs/lib/modules/2.6.10/

```

#### 5.5.4 File System Workflow

Refer to the files under ./mnt\_rootfs/etc/ directory to understand the workflow of a root file sytem. i.e. to change the Ethernet IP address, open and edit the file ./mnt\_rootfs/etc/network/interfaces.

| Document:<br>Document num         | phyCORE-LPC3180 QuickStart Instructions -<br>ber: L-698e_2, June 2007                                       | LINUX |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------|-------|

| How would you im                  | prove this manual?                                                                                          |       |

|                                   |                                                                                                             |       |

|                                   |                                                                                                             |       |

|                                   |                                                                                                             |       |

|                                   |                                                                                                             |       |

| Did you find any n                | istakes in this manual?                                                                                     | page  |

|                                   |                                                                                                             |       |

|                                   |                                                                                                             |       |

|                                   |                                                                                                             |       |

|                                   |                                                                                                             |       |

| Submitted by:<br>Customer number: |                                                                                                             |       |

| Name:                             |                                                                                                             |       |

| Company:                          |                                                                                                             |       |

| Address:                          |                                                                                                             |       |

|                                   |                                                                                                             |       |

| Return to:                        | PHYTEC America LLC<br>203 Parfitt Way SW, Suite G100<br>Bainbridge Island, WA 98110<br>Fax : (206) 780-9135 |       |

Published by

© PHYTEC America LLC 2007

Document Number: L-698e\_2 Printed in Germany